M.Sc. (Computer Science)

Master of Computer Application

MS - 03 / MCA - 203

Course Curriculum for

# Digital Electronics

125001

| Sr. No. | Lesson Name                              | Page No. |

|---------|------------------------------------------|----------|

| 1.      | Introduction                             | 3        |

| 2.      | Binary Algebra                           | 13       |

| 3.      | Logic Gates                              | 34       |

| 4.      | Digital Integrated Circuits              | 60       |

| 5.      | Flip-Flops and Sequential Logic Circuits | 80       |

| 6.      | Applications of Logic Circuits-I         | 118      |

| 7.      | Applications of Logic Circuits-II        | 140      |

: 1

Author: Vetter:

Dr. Devendra Mohan Dr. Sib Krishna Ghoshal

#### Introduction

All of us are familiar with the impact of digital calculators, watches, modern communication systems and computers in every day life. All persons working in various fields related to electronics must understand the performance of Digital Electronic Circuits. All sizes of computers, as we know, perform complicated task with fantastic speed and accuracy. At stores, the cash register read out digital display digital clock and watches flash the time in all city shops and restaurants. Most automobiles use microprocessors to control engine functions. Aircraft's defense sectors, factory machines and modern diagnostic in medical science are controlled by digital circuits.

Therefore, one asks obvious questions like:

- What is a digital circuit?

- How digital circuits work?

- Why use digital circuits?

- How one makes a digital signal? How does one test a digital signal? And so on, a long list of queries.

This revolution took place with the advent of integrated circuits (IC) which is an offspring of semiconductor technology. The inexpensive fabrication of ICs has made the subject Digital Electronics easy to study. One small IC can perform the task of thousands of Transistors Diodes and Resistors. Many ICs are used to construct Digital Circuits. This is an exciting and rapidly growing field, which uses several principles for the working of computers, Communication systems, Digital machinery's etc. The basic idea is to let the beginners understand the operation of the Digital system and many other systems based on the principles of Digital Techniques. Any

device working under Digital Techniques are called Digital Systems and the Electronic Network used to make them operational are called Digital Circuits. The subject as a whole is often referred as **Modern Digital Electronics**.

Electronic circuits use two kinds of signals. They are **Analog Signals** (continuous supply of voltages and currents) and **Digital Signals** (discrete voltages and current). For example, Circuits (electronic network) using Analog signals are known as **Linear or Analog Circuits**. Similarly, the electronic network of an electronic calculator or digital watch that uses Digital signals are called **Digital Circuits**.

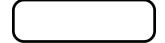

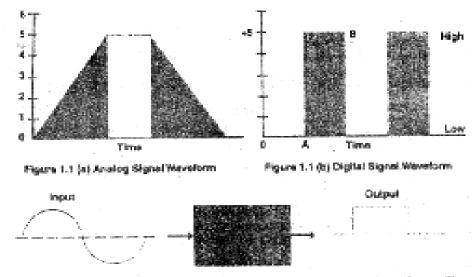

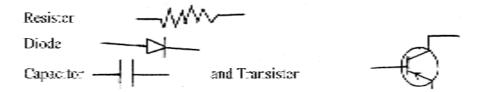

An analog device, then, is one that has a signal, which varies continuously in time with the input, whereas, a digital device operates with a digital signal that varies discontinuously. As a result, the Digital Electronics is the world of **ZEROS'** (OFF/LOW/DOWN/FALSE) and 'ONES' (ON/HIGH/UP/TRUE). Figure 1.1 shows the behavior of Analog and Digital signal and the possibility of conversion from Analog to Digital. Figure 1.2 represents a symbol of some devices using Analog and Digital world. This example is set to explain how real life problem like movement of a pivot on a water tank that indicates the level of water can be translated to analog/digital form.

## **Figure**

Figure 1.1 (c) Block Diagram of Electronic Circuit Shaping a Sine Weve Into a Square Wave

Figure 1.2 Digital System used to Interpret Float Level in Weter Tank

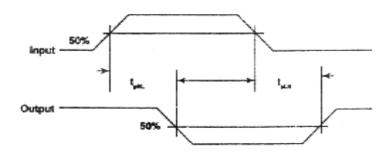

Figure 1.3 Digital Signal Representation

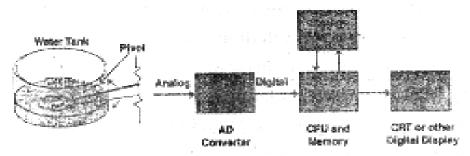

Digital system works under logic and hence they are called **Logic Circuits**, whose building blocks are known as **Gates**. These circuits employ two different representations of digital signal known as Positive Logic Systems and Negative Logic Systems as shown in Figure 1.3. The two discrete signal levels HIGH and LOW are generally represented by **Binary Digits** 1 and 0 respectively is referred to as **bit** and binary number with 8 bits is known as a **byte**.

Since a digital signal can have only one of the two possible level 1 and 0, the **Binary Number System** can be used for the analysis and design of digital system, which was introduced by George Boolean in 1854 and the corresponding algebra is known as **Boolean Algebra**. These logic concepts have been adopted for the design of digital circuit.

The number system that we use in day-to-day life is called **Decimal Number System**. In this system, one works with 10 different Digits, (0 through 9) and is known as based-ten system. But digital electronic devices used a 'strange' number system called **binary**. Digital computers and microprocessor-based systems use other strange

number systems called **Hexadecimal** and **Octal**. One who works in electronics must know how to convert numbers from the everyday decimal system to binary, to Hexadecimal, and to Octal system.

The hexadecimal number system uses the 16 symbol: 0 through 9,A, B, C, D, E, and F and is referred to as base-sixteen system. The letter 'A' stands for decimal 10, 'B' for decimal 11, and so on. The Octal number system uses the 8 symbols: 0 through 7 and are referred to as base-eight system

Any **Decimal number** of any magnitude can be expressed by using the system of positional weighting in which the right most digit of the number called the 'least significant digit' is multiplied by  $10^0$  to the number, the digit left to the least significant digit is multiplied by  $10^1$ . Similarly, as we move in the number towards left side the power increases in steps of 1.

For example in decimal number  $(386)_{10}$  the weightage of digit 6 is  $6x10^0=6$ , the weightage of digit 8 is  $8x10^1=80$  and for digit 3 is  $3x10^2=300$ .

Summing all three values 6, 80, and 300 we get

$$386 = 3 \text{ x hundred} + 8 \text{ x ten} + 6 \text{ x unity}$$

$$= 3x10^{2} + 8x10^{1} + 6x10^{0}$$

$$= 3x100 + 8x10 + 6x1$$

$$= 300 + 80 + 6 = (386)_{10}$$

The **binary number system** is exactly like the Decimal system except that the base is 2 instead of 10. Again each position in a binary number represent a power of the base 2. In this system, the right most position is the unit  $2^{\circ}$  position, the second position from the right is the 2's ( $2^{\circ}$ ), and proceeding in this way, we have 4's ( $2^{\circ}$ ), 8's ( $2^{\circ}$ ) position, and so on.

Thus, the decimal equivalent of the binary number 10101 (written as 10101), is

$$1x2^{4}+0x2^{3}+1x2^{2}+0x2^{1}+1x2^{0}$$

or  $16+0+4+0+1$  or  $21$

Thus, we write  $(10101)_{2} = (21)_{10}$

In the **octal system** the largest single digit is 7 (one less than the base). Again each position an octal number represent a power of the base 8.

Thus the decimal equivalent of the octal number 943 (written as 943)<sub>8</sub> is

$$9x8^{2}+4x8^{1}+3x8^{0}$$

or  $9x64+32+3$

or  $576+32+3$

or  $611$

so we have  $(943)_{8} = (6!!)_{10}$

In hexadecimal system, the largest single digit is F or 15 (one less than the base). Again, each position in a Hexadecimal system represents a power of the base 16.

Thus, the decimal equivalent of the Hexadecimal number 3AF written as  $(3AF)_{16}$  or H is

$$3x16^{2}+Ax16^{1}+Fx16^{0}$$

or

$$3x256+10x16+15x1$$

or

$$768+160+15$$

or

$$943$$

Thus

$$(3AF)_{16}=(943)_{10}$$

And

$$(3AF)_{16}=(1110101111)_{2}$$

The **Binary Coded Decimal (BCD)** Code is one of the early memory codes. It is based on idea of converting each digit of a decimal number into its binary equivalent rather than converting the entire decimal value into a pure binary form.

Converting  $(943)_{10}$  into BCD, results the following

$$(943)_{10} = \underline{1001} \quad \underline{0100} \quad \underline{0011}$$

$9 \quad 4 \quad 3$

or 100101000011 in BCD

Table 1.1 represents binary, hexadecimal, BCD equivalence to decimal numbers and Table 1.2 represent alphabetic and numeric characters in BCD along with their octal equivalent

| Decimal   | Binary | Hexadecimal                | BCD Equivalent |

|-----------|--------|----------------------------|----------------|

| 0         | 0000   | 0                          | 0000           |

| 1         | 0001   | 1                          | 0001           |

| 2         | 0010   | 2                          | 0010           |

| 3         | 0011   | 3                          | 0011           |

| 4         | 0100   | 4                          | 0100           |

| 5         | 0101   | 5                          | 0101           |

| 6         | 0110   | 6                          | 0110           |

| 7         | 0111   | 7                          | 0111           |

| 8         | 1000   | 8                          | 1000           |

| 9         | 1001   | 9                          | 1001           |

| <i>10</i> | 1010   | $oldsymbol{A}$             | 00010000       |

| 11        | 1011   | $\boldsymbol{\mathit{B}}$  | 00010001       |

| 12        | 1100   | $\boldsymbol{\mathcal{C}}$ | 00010010       |

| <i>13</i> | 1101   | D                          | 00010011       |

| 14        | 1110   | $oldsymbol{E}$             | 00010100       |

| <i>15</i> | 1111   | $oldsymbol{F}$             | 00010101       |

| 16        | 10000  | 10                         | 00010110       |

| 17        | 10001  | 11                         | 00010111       |

**Table 1.1**

| Characters       | Code Digit (BCD) | Octal Equivalent |

|------------------|------------------|------------------|

| $\overline{A}$   | 0001             | 61               |

| B                | 0010             | 62               |

| C                | 0011             | 63               |

| D                | 0100             | 64               |

| $\boldsymbol{E}$ | 0101             | 65               |

| F                | 0110             | 66               |

| G                | 0111             | 67               |

| H                | 1000             | 70               |

| I                | 1001             | 71               |

| J           | 0001 | 41 |

|-------------|------|----|

| K           | 0010 | 42 |

| L           | 0011 | 43 |

| M           | 0100 | 44 |

| N           | 0101 | 45 |

| O           | 0110 | 46 |

| P           | 0111 | 47 |

| Q           | 1000 | 50 |

| $\tilde{R}$ | 1001 | 51 |

| S           | 0010 | 22 |

| T           | 0011 | 23 |

| U           | 0100 | 24 |

| V           | 0101 | 25 |

| W           | 0110 | 26 |

| X           | 0111 | 27 |

| Y           | 1000 | 30 |

| Z           | 1001 | 31 |

| 1           | 0001 | 01 |

| 2           | 0010 | 02 |

| 3           | 0011 | 03 |

| 4           | 0100 | 04 |

| 5           | 0101 | 05 |

| 6           | 1001 | 06 |

| 7           | 0111 | 07 |

| 8           | 1000 | 10 |

| 9           | 1001 | 11 |

| 0           | 1010 | 12 |

|             |      |    |

Table 1.2

| Characters | Digit | ASCII-7 code<br>Hexadecimal<br>equivalent | Digit | ASCII-7 code<br>Hexadecimal<br>equivalent |

|------------|-------|-------------------------------------------|-------|-------------------------------------------|

| 0          | 0     | 30                                        | 0     | 50                                        |

| 1          | 1     | 31                                        | 1     | 51                                        |

| 2          | 10    | 32                                        | 10    | 52                                        |

| 3          | 11    | 33                                        | 11    | 53                                        |

| 4          | 100   | 34                                        | 100   | 54                                        |

| 5                      | 101  | 35 | 101  | 55 |

|------------------------|------|----|------|----|

| 6                      | 110  | 36 | 110  | 56 |

| 7                      | 111  | 37 | 111  | 57 |

| 8                      | 1000 | 38 | 1000 | 58 |

| 9                      | 1001 | 39 | 1001 | 59 |

| $\boldsymbol{A}$       | 1    | 41 | 1    | A1 |

| $\boldsymbol{B}$       | 10   | 42 | 10   | A2 |

| $\boldsymbol{C}$       | 11   | 43 | 11   | A3 |

| D                      | 100  | 44 | 100  | A4 |

| $oldsymbol{E}$         | 101  | 45 | 101  | A5 |

| $oldsymbol{F}$         | 110  | 46 | 110  | A6 |

| $\boldsymbol{G}$       | 111  | 47 | 100  | A7 |

| H                      | 1000 | 48 | 1000 | A8 |

| I                      | 1001 | 49 | 1001 | A9 |

| $oldsymbol{J}$         | 1010 | 4A | 1010 | AA |

| K                      | 1011 | 4B | 1011 | AB |

| $oldsymbol{L}$         | 1100 | 4C | 1100 | AC |

| M                      | 1101 | 4D | 1101 | AD |

| N                      | 1110 | 4E | 1110 | Æ  |

| 0                      | 1111 | 4F | 1111 | AF |

| P                      | 0    | 50 | 0    | B0 |

| $\boldsymbol{\varrho}$ | 1    | 51 | 1    | B1 |

| $\boldsymbol{R}$       | 10   | 52 | 10   | B2 |

| $\boldsymbol{S}$       | 11   | 53 | 11   | В3 |

| T                      | 100  | 54 | 100  | B4 |

| $oldsymbol{U}$         | 101  | 55 | 101  | B5 |

| $oldsymbol{V}$         | 110  | 56 | 110  | B6 |

| $oldsymbol{W}$         | 111  | 57 | 111  | В7 |

| $\boldsymbol{X}$       | 1000 | 58 | 1000 | B8 |

| Y                      | 1001 | 59 | 1001 | В9 |

| $\boldsymbol{Z}$       | 1010 | 5A | 1010 | BA |

|                        |      |    |      |    |

# Table 1.3 Represents Numeric and Alphabetic Characters in ASCII- and ASCII-8 Notation along with their Hexadecimal Equivalent

Another important code that is very widely used in computer is the American Standard Code for Information Interchange (ASCII). This code is popular in data communications. ASCII is of two types: ASCII-7 and ASCII-8. ASCII-7 is a 7 bit code that allows 2<sup>7</sup>(128) different characters. ASCII-8 (8bit code) is an extended version of ASCII-7 that allows 28(256) different characters as shown in Table 1.3.

The binary code for the word BOY in ASCII-7 can be represented as

| <u>1000010</u> | <u>1001111</u> | <u>1011001</u> |

|----------------|----------------|----------------|

| В              | O              | Y              |

The first 3 bits in each of the character (for example 100 for B, 100 for O and 101 for Y), are used as 'zone' bits which is internal code for ASCII. In ASCII-8, the representation of BOY will be

The first 4 bit in each of the character are used as zone bits.

It is therefore important to highlight the superiority of digital circuits and systems over the analog circuits. The 'Real-world' information deals with time, speed, weight, pressure, light intensity, and position measurement and is all analog in nature. Digital systems are required when data must be stored, used for calculations, or displayed as numbers/or letters. They are valuable when calculations, data manipulations, and alphanumeric outputs are required. The "Central Processing Unit" (CPU) of a computer can manipulate the input data, output the information, store the information and so forth.

Some of the **advantages** highlighted for the widespread use of digital circuitry in over analog are as follows

- 1. Inexpensive ICs can be used with few external components.

- 2. Operate in one of the two **states**, known as ON and OFF makes it very simple.

- 3. Only a few basic operations are required and are very easy to understand.

- 4. Digital techniques deal with simple logic mathematics called Boolean algebra.

- 5. Operation and network analysis of digital circuitry require simple basic concepts like switching speed and loading on the other hand, analysis of analog circuitry (Involved frequency and time domain) are quite complicated.

- 6. Information can be stored for short periods or indefinitely.

- 7. Data can be used for precise calculations.

- 8. Systems can be designed more easily using compatible digital logic families.

- 9. Systems can be programmed which show some manner of 'intelligence'. A number of programmable ICs are also available.

- 10. The display of data and other information is very convenient, accurate and elegant by using digital techniques.

- 11. Digital circuits have capability of memory, which makes these circuits highly suitable for computers, calculators, watches, telephones, medical diagnostics, etc.

- 12. To learn programming of digital computers it is worth knowing, the way the digital hardware works.

The limitations of digital circuitry are as follows:

Most 'real-world' events are analog in nature.

Analog processing is usually simpler and faster.

Digital circuits are appearing in more and more products primarily because of low-cost, reliable digital ICs. Other reasons for their growing popularity are accuracy, added stability, computer compatibility, memory, ease of use, simplicity of design, and compatibility with at alphanumeric displays.

Author: Vetter:

Dr. Devendra Mohan Dr. Sib Krishna Ghoshal

• Boolean Algebra

- De Morgan's Theorem

- Representation of Boolean Algebra

- De Morgan's Theorem through Logic Circuits

- Karnaugh Map Mathod

- Binary/BCD Subtraction and Addition

## **Boolean Algebra**

Boolean Algebra is Algebra of logic. This is an algebra that deals with logical propositions, which are either true or false. This algebra is suitable for binary number system and is very useful in designing digital circuits, which operates under logic.

For example,

A+A=A, not 2A

Also 1+1 = 1 not 2 as it is logical expression.

One can visualize this as,

TRUE+TRUE=TRUE

FALSE+FALSE=FALSE

A Boolean algebraic expression is composed of variables, constants and operators. The **variables are** generally represented by the letters of the Alphabet (say A) which can have two possible values 1 or 0. The interpretation of 1 may be that

the variable is presented input signal is ON, is TRUE, and is a positive voltage. If A is 0, then it mean that the variable is absent, input signal if OFF, is FALSE, and is a negative voltage. Similarly, the **Boolean Constant** can have any two values, either 1 or 0.

Boolean Operators are used in Boolean Algebra where a mathematical function called **Boolean Function** is constructed. These operators are the Symbols

PLUS (+) meaning an OR operation

DOT (.) meaning and AND operation

BAR 'A read as COMPLEMENT meaning a NOT operation.

## Postulates of Boolean Algebra

A set of Boolean postulates are the following

- (a)  $A = 0 \text{ iff } A \neq 1$  $A = 1 \text{ iff } A \neq 0$

- (b) 0.0=0

- (c) 1+1=1

- (d) 0+0=0

- (e) 1.1=1

- (f) 1.0=0.1=0

- (g) 1+0=0+1=1

The realization of any Boolean Expression can be obtained with the help of a table called **TRUTH TABLE**. To simplify a Boolean Expression, one requires certain laws of Boolean Algebra.

# Laws of Boolean Algebra and their Truth Table

- a) Commutative Law

- i) A+B=B+A

- ii) A.B=B.A

**Truth Table**

| $\boldsymbol{A}$ | В | A+B | A.B | B+A | B.A |

|------------------|---|-----|-----|-----|-----|

| 0                | 0 | 0   | 0   | 0   | 0   |

| 0                | 1 | 1   | 0   | 1   | 0   |

| 1                | 0 | 1   | 0   | 1   | 0   |

| 1                | 1 | 1   | 1   | 1   | 1   |

# b) Associative Law

- i) A+(B+C)=(A+B)+C

- ii) A.(B.C)=(A.B).C

# **Truth Table**

| $\boldsymbol{A}$ | В | C | <i>B</i> + <i>C</i> | A+B | A+(B+C) | (A+B)+C | B.C | A.B | A.(B.C) | (A.B).C |

|------------------|---|---|---------------------|-----|---------|---------|-----|-----|---------|---------|

| 0                | 0 | 0 | 0                   | 0   | 0       | 0       | 0   | 0   | 0       | 0       |

| 0                | 0 | 1 | 1                   | 0   | 1       | 1       | 0   | 0   | 0       | 0       |

| 0                | 1 | 0 | 1                   | 1   | 1       | 1       | 0   | 0   | 0       | 0       |

| 0                | 1 | 1 | 1                   | 1   | 1       | 1       | 1   | 0   | 0       | 0       |

| 1                | 0 | 0 | 0                   | 1   | 1       | 1       | 0   | 0   | 0       | 0       |

| 1                | 0 | 1 | 1                   | 1   | 1       | 1       | 0   | 0   | 0       | 0       |

| 1                | 1 | 0 | 1                   | 1   | 1       | 1       | 0   | 1   | 0       | 0       |

| 1                | 1 | 1 | 1                   | 1   | 1       | 1       | 1   | 1   | 1       | 1       |

# C) Distributive Law

- i) A.(B.C)=(A.B)+(A.C)

- ii) A+(B.C)=(A+B).(A+C)

**Truth Table**

| $\boldsymbol{A}$ | В | C | <i>B</i> + <i>C</i> | A.B | A.C | A.(B+C) | (A.B+A.C) | B.C | A+B | A+C | A+( <b>B.C</b> ) | (A+B).(A+C) |

|------------------|---|---|---------------------|-----|-----|---------|-----------|-----|-----|-----|------------------|-------------|

| 0                | 0 | 0 | 0                   | 0   | 0   | 0       | 0         | 0   | 0   | 0   | 0                | 0           |

| 0                | 0 | 1 | 1                   | 0   | 0   | 0       | 0         | 0   | 0   | 1   | 0                | 0           |

| 0                | 1 | 0 | 1                   | 0   | 0   | 0       | 0         | 0   | 1   | 0   | 0                | 0           |

| 0                | 1 | 1 | 1                   | 0   | 0   | 0       | 0         | 1   | 1   | 1   | 1                | 1           |

| 1                | 0 | 0 | 0                   | 0   | 0   | 0       | 0         | 0   | 1   | 1   | 1                | 1           |

| 1                | 0 | 1 | 1                   | 0   | 1   | 1       | 1         | 0   | 1   | 1   | 1                | 1           |

| 1                | 1 | 0 | 1                   | 1   | 0   | 1       | 1         | 0   | 1   | 1   | 1                | 1           |

| 1                | 1 | 1 | 1                   | 1   | 1   | 1       | 1         | 1   | 1   | 1   | 1                | 1           |

# De Morgan's Theorem

This is a useful theorem in Boolean Algebra which states how to complement a Boolean expression. They allow us to convert back and forth from minterm to maxterm forms of Boolean expression. It helps to eliminate long over-bars that cover several variables.

## a) First Theorem

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

(For two variables)

In general  $\overline{A + B + C} + \dots = \overline{A} \cdot \overline{B} \cdot \overline{C} \cdot \dots$  (For many variables)

# b) Second Theorem

$$\overline{A} \cdot \overline{B} = \overline{A} + \overline{B}$$

In general  $\overline{A}$ ,  $\overline{B}$ ,  $\overline{C} = \overline{A} + \overline{B} + \overline{C} + \dots$

## **Truth Table**

| A | В | $\overline{\mathbf{A}}$ | $\overline{\mathbf{B}}$ | AB | A + B | $\overline{A+B}$ | $\overline{\mathbf{A}.\mathbf{B}}$ |

|---|---|-------------------------|-------------------------|----|-------|------------------|------------------------------------|

| 0 | 0 | 1                       | 1                       | 0  | 0     | 1                | 1                                  |

| 0 | 1 | 1                       | 0                       | 0  | 1     | 0                | 0                                  |

| 1 | 0 | 0                       | 1                       | 0  | 1     | 0                | 0                                  |

| 1 | 1 | 0                       | 0                       | 1  | 1     | 0                | 0                                  |

# Representation of Boolean Algebra

# & De Morgan's Theorem through Logic Circuits

There are nine basic identities commonly used in converting complex Boolean expression to their simple forms. A Boolean identity usually consists of one variable and one constant equates two expressions, which are equal for all possible combinations of the variables. The equivalence of two expressions is presented through Truth Table and representative circuits symbol.

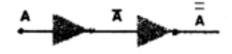

# **Double Complementation**

A double complementation is the complementation of a single complement. The single complement is called **NOT** operation.

Expression:  $\overline{A} = A$

#### **Truth Table**

| $\mathbf{A}$ | $\overline{\mathbf{A}}$ | A |

|--------------|-------------------------|---|

| 0            | 1                       | 1 |

| 1            | 0                       | 1 |

The triangle with a circle at the vertex is known as **inverter.** This circle is called '**Bubble**' and the expression for output A is read as 'A complement' or 'A NOT'.

In the language of logic gate, this is called NOT Gate. The equivalent inverter symbol looks like

## **AND Function Identities**

The identity states that

$$A.1 = A$$

Corresponding Truth Table and circuit are given below

| A | 1 | Y |

|---|---|---|

| 0 | 1 | 0 |

| 1 | 1 | 1 |

The Boolean expression for the output is A.1, which is read as 'A and 1". In genral this is A.B.

Similarly, there are other identities using AND operator.

i) A.0=0

| A | 0 | Y |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 0 |

i) A.A=A

| A | A | Y |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 1 | 1 |

i) A.Ā=0

| A | $\overline{\mathbf{A}}$ | Y |

|---|-------------------------|---|

| 0 | 1                       | 0 |

| 1 | 0                       | 0 |

# **OR Function Identities**

This identity can be realized with one input permanently tied to logic 1 and the other is varying

A+1=1

| A | 1 | Y |

|---|---|---|

| 0 | 1 | 1 |

| 1 | 1 | 1 |

Other three identities using OR operator are

$i) \qquad A+0=A$

| A | 0 | Y |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

ii) A+A=A

| A | 0 | Y |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

iii)  $A + \overline{A} = 1$

| A | 0 | Y |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

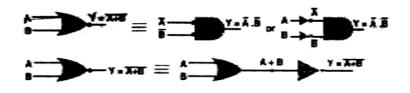

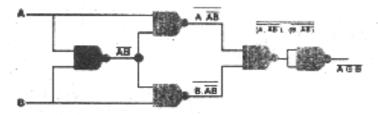

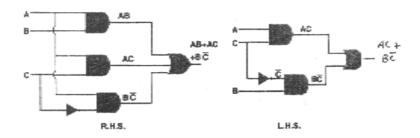

# The Circuit Representation of De Morgan's Theorem

1. A+B = A.B known as NOR circuit, which is equivalent to Bubbled input AND circuit.

| A | В | A+B | $\overline{\mathbf{A}}+\overline{\mathbf{B}}$ | $\overline{\mathbf{A}}$ | B | $\overline{\mathbf{A}} \cdot \overline{\mathbf{B}}$ |

|---|---|-----|-----------------------------------------------|-------------------------|---|-----------------------------------------------------|

| 0 | 0 | 0   | 1                                             | 1                       | 1 | 1                                                   |

| 0 | 1 | 1   | 0                                             | 1                       | 0 | 0                                                   |

| 1 | 0 | 1   | 0                                             | 0                       | 1 | 0                                                   |

| 1 | 1 | 1   | 0                                             | 0                       | 0 | 0                                                   |

2.  $= \overline{A} + \overline{B}$  known as NAND circuit, which is equivalent to Bubbled input OR circuit.

| A | В | A.B | A.B   | Ā | $\overline{\mathbf{B}}$ | $\overline{\mathbf{A} + \mathbf{B}}$ |

|---|---|-----|-------|---|-------------------------|--------------------------------------|

| 0 |   |     | 1     |   |                         | 1                                    |

| 0 | 1 | 0   | 1 A.B | 1 | 0                       | 1                                    |

| 1 | 0 | 0   | 1     | 0 | 1                       | 1                                    |

| 1 | 1 | 1   | 0     | 0 | 0                       | 0                                    |

## Karnaugh Map Method

There are two methods for developing the required logic diagram from a given Truth Table. The first method requires "Boolean Algebra" and "De Morgan's Theorem" to reduce the expressions produced to lowest term (Minimal expressions). The second method is a variation of the first and uses a tool called the "Karnaugh Map (K-Map)". The K-Map is the simple3st and most commonly used method. It is a graphical method (in the form of table) extensively used to simplify Boolean equation.

The K-Map method uses a table or map to reduce its expressions. Each position in the table is called a "CELL". CELLs are filled with ones and zeros according to the expressions to be reduced.

Adjacent ones are grouped together in clusters, called "subcobes", following definite rules: a subcube must be of size 1,2,4,8,16, etc. All 1s must be included in a subcube of maximum size. These rules are explained through examples below

Assignment 1

Designed a circuit that will behave according to this Truth Table

| Inputs |   |   | Output                                         |

|--------|---|---|------------------------------------------------|

| C      | В | A | Y                                              |

| 0      | 0 | 0 | 0                                              |

| 0      | 0 | 1 | 0                                              |

| 0      | 1 | 0 | 1                                              |

| 0      | 1 | 1 | 1                                              |

| 1      | 0 | 0 | 0                                              |

| 1      | 0 | 1 | 0                                              |

| 1      | 1 | 0 | 1                                              |

| 1      | 1 | 1 | $\overline{\mathbf{C}}\overline{\mathbf{B}}$ 1 |

# **Solution**

**Step 1.** Draw the table. Choose two of the variables to use as column headings across the top. We will chose C and B. From all combinations of C and 'C with B and 'B. Each column heading should differ from all adjacent column by one variable only.

| Part 1 | $\overline{\mathbf{C}} \ \overline{\mathbf{B}}$ | $\overline{\mathbf{C}}$ B | СВ |  |

|--------|-------------------------------------------------|---------------------------|----|--|

|        |                                                 |                           |    |  |

|        |                                                 |                           |    |  |

Start with  $\overline{C}$   $\overline{B}$  and change  $\overline{B}$  to B to from the heading for column 2,

Then change  $\overline{C}$  to C for the third column CB, and finally . The fourth (22)

column wraps around to the first column and should differ by one variable only, which it does.

| Part 1 | $\overline{\mathbf{C}} \ \overline{\mathbf{B}}$ | $\overline{\mathbf{C}}$ B | C B |  |

|--------|-------------------------------------------------|---------------------------|-----|--|

|        |                                                 |                           |     |  |

|        |                                                 |                           |     |  |

Use the third variable, A for row headings  $\overline{A}$  and A.

Step 2. Fill the table with ones and zeros from the Truth Table. The output Y is 1 in line 3 when we have and B and . Place a 1 in the table in cell B. The output Y is also 1 on line 4, which is represented by BA, on line 6, which is C. A, on line 7, whichis CB., and on line 8, which is CBA. Fill those cells with ones and the remaining cells with zeros.

**Step 3.**Combine adjacent cells that contain ones in sub cubes of maximum size. The four ones in the centre of the table compose a sub cube of size 4.

| Part 1 | $\overline{\mathbf{C}} \ \overline{\mathbf{B}}$ | $\overline{\mathbf{C}}$ <b>B</b> | СВ |   |

|--------|-------------------------------------------------|----------------------------------|----|---|

|        | 0                                               | 1                                | 1  | 0 |

|        | 0                                               | 1                                | 1  | 1 |

The 1 in cell  $\overline{CB}$  A has not been included in a sub cube so it is used with its adjacent 1 in a sub cube of size 2.

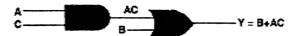

**Step 4.** Write the expression that 3ach sub cube represents. In the sub cube of size 4, find the variable that occurs in all four cells. In these case B is the only variable that appears in all four cells. The sub cube of size 4 represents B. In the sub cube of size two, A and C appear in each cell, so the sub cube represents AC.

**Steps 5.** From the output expression. The output Y is the expression from each sub cube ORed together. In this case Y=B+AC.

The Truth Table can be implemented by the above logic diagram.

#### Verification

In the circuit, when A and C are both 1s, the output of the AND will also be 1. A 1 into an OR gives a 1 out. In the Truth Table, A and C are both 1s on line6 and 8, and the required output is 1. In the circuit, any time B is 1 the output is 1. In the Truth Table, B is 1 on lines 3, 4, 7 and 8, and the required output is 1. The rest of the time both inputs into the OR gate will be 0, and the result will be 0. This occur on lines of 1, 3 and 5 of the Truth Table where the output is 0. In all cases the circuit produces the results required by the Truth Table.

## **Assignment 2**

Use a Karnaugh map to design a logic diagram to implement the following Truth Table.

## **Inputs Output**

| Inputs |   |   | Output |

|--------|---|---|--------|

| C      | В | A | Y      |

| 0      | 0 | 0 | 0      |

| 0      | 0 | 1 | 1      |

| 0      | 1 | 0 | 0      |

| 0      | 1 | 1 | 0      |

| 1      | 0 | 0 | 0      |

| 1      | 0 | 1 | 1      |

| 1      | 1 | 0 | 1      |

| 1      | 1 | 1 | 1      |

# **Solution**

**Step 1.** Draw the table.

| $\overline{\mathbf{C}} \ \overline{\mathbf{B}}$ | $\overline{\mathbf{C}}$ <b>B</b> | C B |   |

|-------------------------------------------------|----------------------------------|-----|---|

| 0                                               | 1                                | 1   | 0 |

| 0                                               | 1                                | 1   | 1 |

- **Step 2.** Fill the table with 1s and 0s from the Truth Table.

- **Step 3.** Combination adjacent cells that contain 1s into sub cubes (size 1, 2, 4, or 8).

| $\overline{\mathbf{C}} \ \overline{\mathbf{B}}$ | $\overline{\mathbf{C}}$ B | C B |   |

|-------------------------------------------------|---------------------------|-----|---|

| 0                                               | 0                         | 1   | 0 |

| 1                                               | 0                         | 1   | 1 |

The right side of the table "wraps around" to the other side so that the table is continuos. The  $1e^{i}\overline{\mathbf{p}}$  the lower corners from a sub cube of size 2. The two sub cube "cover" the map in that all 1s are contained in sub cube. Any additional sub cube drawn would add un-needed terms to the final expression.

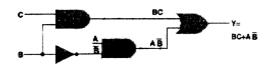

- **Step 4.** Write the expression that each sub cube represents. In the vertical sub cube, C and B remain constant. In the horizontal sub cube, 'B and A are constant.

- **Step 5.** From the output expression.

$$Y = BC + Y = BC + A\overline{B}$$

# **Assignment 3**

Use a Karnaugh map to design a logic diagram to implement the following Truth Table.

| Inpu | ıts |   |   | Output                                   |

|------|-----|---|---|------------------------------------------|

| D    | C   | В | A | Y                                        |

| 0    | 0   | 0 | 0 | 1                                        |

| 0    | 0   | 0 | 1 | 0                                        |

| 0    | 0   | 1 | 0 | 1                                        |

| 0    | 0   | 1 | 1 | 0                                        |

| 0    | 1   | 0 | 0 | 0                                        |

| 0    | 1   | 0 | 1 | 1                                        |

| 0    | 1   | 1 | 0 | 0                                        |

| 0    | 1   | 1 | 1 | 0                                        |

| 1    | 0   | 0 | 0 | 1                                        |

| 1    | 0   | 0 | 1 | 0                                        |

| 1    | 0   | 1 | 0 | 1                                        |

| 1    | 0   | 1 | 1 | $\mathbf{D} \ \overline{\mathbf{C}} \ 0$ |

| 1    | 1   | 0 | 0 | 1                                        |

| 1    | 1   | 0 | 1 | 1                                        |

| 1    | 1   | 1 | 0 | 1                                        |

| 1    | 1   | 1 | 1 | 1                                        |

# **Solution**

**Step 1.** Draw the table. Since four variables are needed, use two across the top and down the side.

| $\overline{\mathbf{D}}  \overline{\mathbf{C}}$ | $\overline{\mathbf{D}}$ C | DC |   |

|------------------------------------------------|---------------------------|----|---|

| 1                                              | 0                         | 1  | 1 |

| 0                                              | 1                         | 1  | 0 |

| 0                                              | 0                         | 1  | 0 |

| 1                                              | 0                         | 1  | 1 |

- **Step 2.** Fill the table with 1s and 0s from the truth Table.

- Step 3. Combine adjacent cells that contain 1s into subcubes of size 1, 2, 4, 8 or 16.

| $\overline{\mathbf{D}}  \overline{\mathbf{C}}$ | $\overline{\mathbf{D}}$ C | DC |   |

|------------------------------------------------|---------------------------|----|---|

| 1                                              | 0                         | 1  | 1 |

| 0                                              | 1                         | 1  | 0 |

| 0                                              | 0                         | 1  | 0 |

| 1                                              | 0                         | 1  | 1 |

Since the map is continuous top to bottom and side to side, the four corners are adjacent and form a sub cube of size 4. The DC column forms another sub cube of size 4. One cell remains uncovered. 'DC'BA forms a sub cube of size 2 with the cell on its right.

**Step 4.** Write the expression that each sub pure represents. The sub cube formed by the four corners represents the term 'A'C. The vertical sub cube represents the expression CD, and the sub cube of size 2 represents the expression A'BC.

**Step 5.** From the output expression.

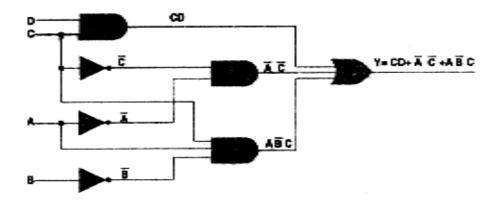

$$Y = CD + \overline{A} \overline{C} + A \overline{B} C$$

## **Binary/BCD Subtraction and Addition**

Write working with digital equipment, one has to convert from the binary code to decimal numbers. If a binary number, say 110011 is given, what would be it equals in decimal? First write down the binary numbers as

## **Binary**

#### **Decimal**

$$1x2^5 + 1x2^4 + 0x2^3 + 0x2^2 + 1x2^1 + 1x2^0$$

or

$$32+16+0+0+2+1$$

or 51

Shortly, it is written as

$$(110011)_2 = (51)_{10}$$

In another example,  $(101010)_2 = (?)_{10}$

# **Binary**

#### **Decimal**

$$1x2^5 + 0x2^4 + 1x2^3 + 0x2^2 + 1x2^1 + 0x2^0$$

or

$$32+0+8+0+2+0$$

or 42

Thus,  $(101010)_2 = (42)_{10}$

What about  $(1101010.101)_2 = (?)_{10}$

## Binary

| 1        | 1        | 0 | 1 | 0 | 1 | 0 | • | 1 | 0 | 1 |

|----------|----------|---|---|---|---|---|---|---|---|---|

| Docition | <b>.</b> |   |   |   |   |   |   |   |   |   |

#### Position

6 5 4 3 2 1 0 -1 -2 -3

#### **Decimal**

$$1x2^{6}+1x2^{5}+0x2^{4}+1x2^{3}+0x2^{2}+1x2^{1}+0x2^{0}\cdot 1x2^{-1}+0x2^{-2}+1x2^{-3}$$

or

$$64+32+0+8+0+2+0.1/_{2}+0/_{4}+1/_{8}$$

or

$$106(5/_{8}) \text{or } 106.625$$

Thus

$$(1101010.101)_2 = (106.625)_{10}$$

Now, let us look at the method of converting decimal number to binary number.

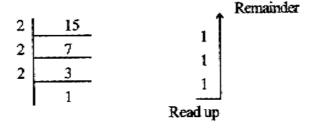

The most popular method to convert decimal number to binary number is the "DOUBLE-DABBLE" method. In this method, one progressively divides the given decimal number by 2 and writes down the remainder after each division. The remainder is read in reverse order.

However, to convert a fraction number into binary number, multiply the decimal number by 2 and record the carry in the integer position and down ward read these carries. Let us take few examples to understand the method of conversion.

## **Assignment 4**

$$(15)_{10} = (?)_2$$

#### **Solution**

$$(15)_{10} = (1111)_2$$

## **Assignment 5**

$$(.35)_{10} = (?)_2$$

#### **Solution**

0.35x2=0.70 with a carry 0

0.70x2=1.40 with a carry 1

0.40x2=0.80 with a carry 0

$$0.80x2=1.60$$

with a carry 1

$0.60x2=1.20$  with a carry 1

$0.20x2=0.40$  with a carry 0  $\rightarrow$  **Stop when the number started repeating**

$(.35)_{10}=(.010110...)_2$

## **Binary Addition**

Binary addition is performed in the same manner as decimal Addition. However, since Binary system has only two digits, the addition table for Binary Arithmetic is very simple consisting of only four entries.

The complete table for Binary addition is as follows;

0+0=0

0+1=1

1+0=1

1+1=0 plus a carry of 1 to next higher column

Alternately, 1+1=10 (sum 0 with carry 1)

Carry-overs are performed in the same way as in decimal arithmetic.

Since 1 is the largest digit in Binary system, any sum greater than 1 requires that a digit be carried over. For instance, 10 plus 10 binary requires the addition of two 1's in the second position. Since 1+1=0 plus a carry over1, the sum of 10+10 is 100 in binary.

# **Assignment 6**

$$(1010)_2 + (101)_2 = (1111)_2$$

#### **Solution**

| Binary                     | Decimal            |

|----------------------------|--------------------|

| (1010) <sub>2</sub>        | (10) <sub>10</sub> |

| <u>+(101)</u> <sub>2</sub> | $\pm (5)_{10}$     |

| $(1111)_2 =$               | $(15)_{10}$        |

# **Assignment 7**

$$(1011)_2 + (111)_2 = (10010)_2$$

#### **Solution**

Binary Decimal

$$(1011)_2$$

Carry bits $(1+1+1=11)$   $(11)_{10}$   $\pm (111)_2$   $\pm (7)_{10}$   $(10010)_2$  =  $(18)_{10}$

## **Assignment 8**

$$(100011)_2 + (11011)_2 = (1000010)_2$$

## **Solution**

Binary Decimal

1111 Carry bits

$$(39)_{10}$$

$(100011)_2$   $(27)_{10}$

$+(11011)_2$

$(1000010)_2$  =  $(66)_{10}$

## **Binary Subtraction**

The principle of binary subtractions consists of two steps. The first step is to determine if it is necessary to borrow. If the subtrahend (the lower digit) is larger than the minuend (the upper digit), it is necessary to borrow from the column to the left. It is important to note here that the value borrowed depends on the base of the number and is always the decimal equivalent of the base. Thus, in decimal, 10 is borrowed; in binary, 2 is borrowed. The second step is simply to subtract the lower value from the upper value.

The complete table for binary subtraction is as follows

$$0 - 0 = 0$$

$$1-0=1$$

0-1=1 with a borrow from the next column.

# Alternately, 10-1=1

Note that the only case in which it is necessary to borrow is when 1 is subtracted from 0. Let us take few more examples to make the operation more clear

# **Assignment 9**

$$(10101)_{2}$$

- $(01110)_{2}$ = $(0011)_{2}$

## **Solution**

| Binary                        | Decimal                   |

|-------------------------------|---------------------------|

| 12                            |                           |

| 0202 borrow                   |                           |

| (10101) <sub>2</sub>          | (21) <sub>10</sub>        |

| <u>-(01110)</u> <sub>2</sub>  | <u>(14)</u> <sub>10</sub> |

| <u>(00111)</u> <sub>2</sub> = | <u>(7)</u> <sub>10</sub>  |

# **Assignment 10**

$$(10100)_{2}$$

- $(1111)_{2}$ = $(00101)_{2}$

## **Solution**

| Binary                      | Decima                    |

|-----------------------------|---------------------------|

| 01212 borrow                |                           |

| (10100) <sub>2</sub>        | (20) <sub>10</sub>        |

| <u>-(1111)</u> <sub>2</sub> | <u>(15)</u> <sub>10</sub> |

| $(00101)_2 =$               | $(5)_{10}$                |

# **Assignment 11**

$$(101.01)_{2}$$

- $(010.11)_{2}$ = $010.10$

# **Solution**

| Binary                        | Decimal              |  |  |

|-------------------------------|----------------------|--|--|

| 0202 borrow                   |                      |  |  |

| (101.01) <sub>2</sub>         | (5.25) <sub>10</sub> |  |  |

| <u>-(010.11)</u> <sub>2</sub> | (2.75) <sub>10</sub> |  |  |

| $(010.10)_2 =$                | $(2.50)_{10}$        |  |  |

# Exercise

# **Truth Table**

| C | В | $\mathbf{A}$ | $\mathbf{Y}$ |

|---|---|--------------|--------------|

| 0 | 0 | 0            | 0            |

| 0 | 0 | 1            | 1            |

| 0 | 1 | 0            | 0            |

| 0 | 1 | 1            | 0            |

| 1 | 0 | 0            | 0            |

| 1 | 0 | 1            | 1            |

| 1 | 1 | 0            | 1            |

| 1 | 1 | 1            | 1            |

- 1. Use the Boolean algebra method to develop a circuit to implement the truth table above.

- 2. Use the Karnaugh map method to develop a circuit to implement the truth table above.

Author: Vetter:

Dr. Sib Krishna Ghoshal Dr. Devendra Mohan

- 3.1 AND, OR and NOT Gates

- 3.2 NAND, NOR, EXOR and EXNOR Gates

- 3.3 Application: Logic Implementation using Gates

- 3.4 Problems and solutions

#### Introduction

The term "Logic" is generally used to refer a decision-making process. A logic gate, then is a circuit that can decide to say Yes or No at the output based upon the inputs. Gates are circuits that are used to combine digital logic levels (ones and zeros0 in specific ways. The basic building block of any digital circuit is a **logic gate**. A system called **Boolean Algebra** and the corresponding *tabular* representation called Truth Table is used to express the output in terms of the inputs.

Gate is a digital circuit with one or more input signals but with only one output signal. Gate is an electronic switching circuit, which allows passing of the applied input signal under certain specified logical conditions.

The basic gates are AND, OR and NOT gates. An AND gate, universal logic gates NAND and NOR are made. The NAND gate is a NOT gate followed by an AND gate. Similarly, a NOR gate is a NOT gate followed by a OR gate. There are two other basic logic gates called Exclusive OR gate (EXOR) and Exclusive NOR gate (EXNOR).

#### 3.1 AND, OR and NOT Gates

#### **AND Gate**

The AND gate is sometimes called the "All or nothing gate". It has N inputs (N<sup>3</sup>2) and one output. It generates an output signal of 1 only if all input signals are

also1. These basic idea of the AND gate can be realised using simple switches called electrical analog circuit of logical digital AND gate.

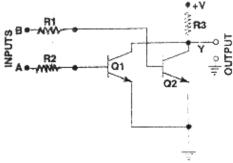

Here two switches A and B are connected in series. One must close both switches A and N to get the lamp to light. There will be no output (that is the bulb will not glow) if either one or both switches are in the OFF (zero) state. So, two or more switches connected in series behave as an AND gate. The AND gates are constructed of diodes and transistors and package inside an IC. The logic symbol of AND gate is shown in Figure 3.2 and the corresponding Truth Table is in Table 3.1.

| Inputs  |        |         |        | Output |        |

|---------|--------|---------|--------|--------|--------|

| В       |        | A       |        | Y      |        |

| Switch  | Binary | Switch  | Binary | Light  | Binary |

| Voltage |        | Voltage |        |        |        |

| Low     | 0      | Low     | 0      | No     | 0      |

| Low     | 0      | High    | 1      | No     | 0      |

| High    | 1      | Low     | 0      | No     | 0      |

| High    | 1      | High    | 1      | Yes    | 1      |

Table 3.1: AND Gate Truth Table

The Boolean expression for a two-input AND gate, with input A and B and output Y is written as

Y=A.B

Which is read "A AND B". The output Y is one only when both A and B are ones. All possible input combinations are listed in the Truth table by counting in binary from 0.0 to 1.1.

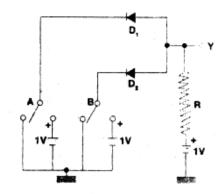

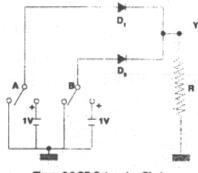

The practical AND gate circuit is shown in Figure 3.3.

Figure 3.3 AND Gate using Diodes

A and B represent the two inputs and Y the output of the AND gate. Suppose that the diodes are ideal and that the two input voltages are either 0 or 1 volt.

Then four cases may arise

- i) Both A= 0V, and B=0V. Under this condition, both the inputs are short-circuited to ground. The 1V battery in the output side, however, biases the two diodes in the forward direction. Hence the two diodes are on, i.e., shorted. The output is also shorted to ground through the diodes. Thus the output Y=0V.

- ii) A=0V, B=1V. In this the upper diode conducts and the output is short-circuited to ground through this diode. Thus Y=0V.

- iii) A=1V, B=0V. In this case, the output is short-circuited to ground through the lower diode and Y=0V.

- iv) Both A=1V and B=1V. Under this condition, none of diodes conduct. Hence no current flows through R. The output is thus held at 1V. Therefore, Y=1V

#### **OR Gate**

The OR gate is sometimes called the "any or all gate". This gate is the physical realization of the logical addition operation. It has N inputs (N<sup>3</sup>2) and one output. The output of an OR gate is 1 only if one or more inputs are 1. The basic idea can be illustrated using simple switches called electrical analog of digital OR operation (Figure 3.4). The Figure shows that the output lamp will light when either or both of the input switches are closed but not when both open.

|         | Inp    | Out     | tput   |       |        |

|---------|--------|---------|--------|-------|--------|

| В       |        | A       | 1      | 7     | Y      |

| Switch  | Binary | Switch  | Binary | Light | Binary |

| Voltage |        | Voltage |        |       |        |

| Low     | 0      | Low     | 0      | No    | 0      |

| Low     | 0      | High    | 1      | No    | 0      |

| High    | 1      | Low 0   |        | No    | 0      |

| High    | 1      | High    | 1      | Yes   | 1      |

**Table 3.2: OR Gate Truth Table**

Figure 3.4 (a) OR Circuit using Switches

The logic symbol (Boolean expression) for the two input OR gates can be represented as:

### Y=A+B

Which is read "A OR B". The Truth Table (Table 3.2) is said to describe inclusion **OR function**.

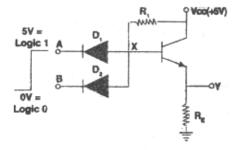

The output Y is 1 when A is 1 or B is 1 or both. The practical OR gate circuit is shown in Figure 3.5.

Figure 3.5 OR Gate using Di-

A and B represent the two inputs and Y the output of the OR gate. The resistor R is the output load resistor. Suppose that the diodes are ideal and that the two input voltages are either 0 or 1V.

Thus, there are four possibilities in which the input voltages may appear. These are,

- i) Both A=0V, and B=0V. Under this condition, none of the diodes conduct and the output Y-0V.

- ii) A=0V, B=1V. Under this condition, the lower diode is forward biased and hence it conducts. The whole of the input voltage appears at the output, since the diode forward resistance is assumed to be negligible. Therefore, Y=1V.

- iii) A=1V or B=0V. In this case, the upper diode conducts and the output Y=1V

- iv) Both A=1V and B=1V. Under this condition bothdiodes are forward-biased and they conduct. The output is held at Y=1V since the voltages are in parallel.

#### **NOT Gate**

The NOT gate is the physical realisation of the complementation operation. This is, an electronic circuit that generates an output signal which is the reverse or inverse of the input signal. A NOT gate is also known as inverter because it inverts the input. The NOT circuit, however, has only one input and one output. The logic symbol for the inverter (NOT gate) is shown in Figure 3.6(a).

| Inputs  |        | Output  |        |  |

|---------|--------|---------|--------|--|

| A       |        | Y       |        |  |

| Voltage | Binary | Voltage | Binary |  |

| Low     | 0      | High    | 1      |  |

| High    | 1      | Low     | 0      |  |

Table 3.3 Truth Table for an Inverter

The Boolean expression for NOT gate is written as

Y = NOTA

= That read as "Y equals not A" or "Y equals complement of A"

The Truth Table is given in Table 3.3

The small circle on the output of the symbol is called a bubble. The bubble on the output indicates that the output is **Active Low**, and the absence of a bubble in the input indicates that the input is active high. The input is "looking for" a 1 level to produce a 0, **Active Low** output.

Therefore, one can say that when a signal passes through an inverter or complimented. We can also say it is **negated**. The terms "**negated**". "**Complemented**", and "**inverted**", then used in the same connotations. The practical NOT gate circuit is shown in Figure 3.6 (b).

If the input voltage is high enough to saturate the transistor, the output is held at a low value. On the other hand, if the input voltage is low enough, the transistor becomes cut-off and the output is high.

### 3.1 NAND, NOR, EXOR and EXNOR Gates

#### **NAND** Gate

A NAND gate is a complemented AND gate. The NOT-AND operation is known as the NAND operation. It is an AND gate followed by a NOT gate. It has N-inputs (N<sup>3</sup>2) and one output. The output of NAND gate will be a 1 if any one of the input is 0 and will be 0 only when all the inputs are 1. The operation of this circuit can be described by the Boolean expression,

$$Y = \overline{A} \cdot \overline{B}$$

$=\overline{A}+\overline{B}$  (using De Morgan's law).

The expression is read as "Y equals NOT) A AND B)"

The Truth Table and the circuit symbol is projected below in Table 3.4 and Figure 3.7 respectively.

The little bubble (called invert bubble) on the right end of the symbol means to invert the AND.

| Inputs |   | Output |      |  |

|--------|---|--------|------|--|

| В      | A | AND    | NAND |  |

| 0      | 0 | 0      | 1    |  |

| 0      | 1 | 0      | 1    |  |

| 1      | 0 | 0      | 1    |  |

| 1      | 1 | 1      | 0    |  |

Table 3.4: Truth Table for AND and NAND Gate

#### **NOR Gate**

A NOR gate is a complemented OR gate. It is an OR gate followed by a NOT gate. The NOR gate is actually a NOT-OR operation. In other words, the output of a OR gate is inverted to form a NOR gate. Figure 3.8 shows an 2 input (N=2) OR gate followed by a NOT gate, that is NOR gate. The Boolean expression for NOR operation is given by.

= A.B (using De Morgan's Law)

$$Y + \overline{A + B}$$

The expression is read as "Y equals NOT (A OR B)"

| Inp | outs | Output |     |  |

|-----|------|--------|-----|--|

| В   | A    | OR     | NOR |  |

| 0   | 0    | 0      | 1   |  |

| 0   | 1    | 1      | 0   |  |

| 1   | 0    | 1      | 0   |  |

| 1   | 1    | 1      | 0   |  |

Table 3.5: Truth Table for OR and NOR Gate

The Truth Table of a Two-input NOR gate is shown in Table 3.5. The output of a NOR gate will be a 1 only when all inputs are 0 and it will be a 0 if any input represents a 1.

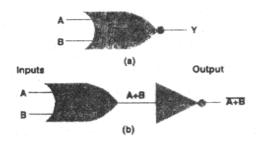

The logic symbol of a two input NOR gate circuit is shown in Figure 3.8 (a).

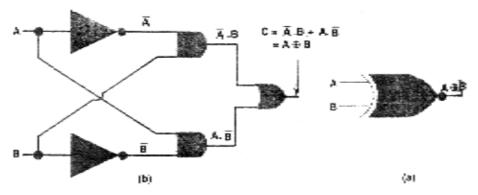

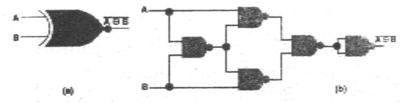

#### **EX-OR Gate**

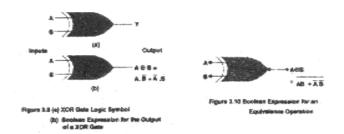

The EXCLUSIVE-OR (EX-OR or XOR) gate is sometimes referred to as the

"Any but not all gate". It is not a basic operation and can be performed using the basic gates-AND, OR and NOR or Universal gates-NAND or NOR.

The logic symbol for the two-input XOR gate and its EQUIVALENCE are diagrammed in Figures 3.9 and 3.10 respectively.

The Boolean expression for the XOR function is

and it is EQUIVALENCE is denoted by

Y = A.B

The Truth Table for the XOR and its equivalence operations are represented in Table 3.6.

| Inputs |                |   | Outp | out |   |

|--------|----------------|---|------|-----|---|

| A      | $\overline{A}$ | В |      |     |   |

| 0      | 1              | 0 | 1    | 0   | 0 |

| 0      | 1              | 1 | 0    | 1   | 1 |

| 1      | 0              | 0 | 1    | 1   | 1 |

| 1      | 0              | 1 | 0    | 0   | 0 |

Table 3.6: Truth Table for OR and XOR Gate

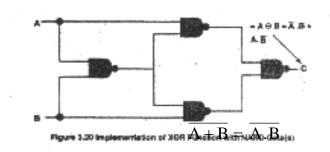

#### **EX-NOR Gate**

The EXCLUSIVE-NOR gate is often shortened to EX-NOR or XNOR gate. The two-input EXNOR gate in shown in Figure 3.11. This is the EX-OR symbol with the added invert bubble on the output side.

The Boolean expression for the EX-NOR function is

$$= \overline{\overline{A}.B + A.\overline{B}}$$

$$= (\overline{\overline{A}.B)(\overline{A}\overline{B})$$

$$= (\overline{A} + \overline{B})(\overline{A} + B) + A\overline{A} + \overline{A}\overline{B} + B\overline{B} + AL$$

$$= \overline{A}.\overline{B} + AB$$

Inputs

(a) Output

(b) (b)

(b) (b)

(c) (d) NAON Gain Logic Symbol Figure 3.11 (a) XNOR Gain Logic Symbol Figure 3.11 (b) Boolean Expression for the Output of a XNOR Gain Logic Symbol Gain Logic Symbol Figure 3.11 (b) Boolean Expression for the Output of a XNOR Gain Logic Symbol Gain Logic Symbol Gain Logic Symbol Figure 3.11 (b) Boolean Expression for the Output of a XNOR Gain Logic Symbol Symbol

The bar over  $A \oplus B$  expression tells us we have inverted the output of XOR gate. The Truth Table is examined in Table 3.7. Notice that the output of the XNOR gate is the complement of the XOR Truth Table.

| Inputs | S | Output |      |                                            |

|--------|---|--------|------|--------------------------------------------|

| В      | A | XOR    | XNOR |                                            |

| 0      | 0 | 0      | 1    |                                            |

| 0      | 1 | 1      | 0 Y  | $=\overline{\mathbf{A} \oplus \mathbf{B}}$ |

| 1      | 0 | 1      | 0    |                                            |

| 1      | 1 | 1      | 0    |                                            |

Table 3.7: Truth Table for XOR and XNOR Gate

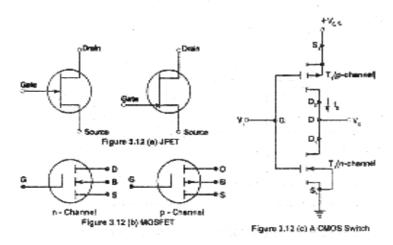

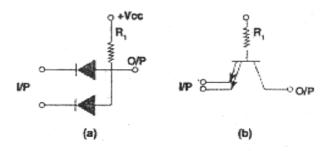

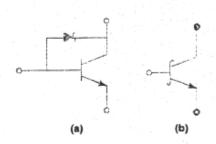

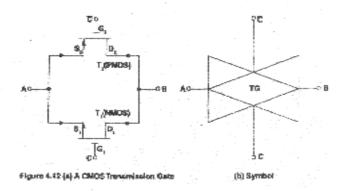

#### **CMOS Gate**

The CMOS (Complementary Metal Oxide Semiconductor) is actually a complementary metal oxide Semiconductor Field Effect Transistor (MOSFET) which is obtained by connecting a p-channel and an n-channel MOSFET in series. The circuit symbol for FET and MOSFET is shown in Figure 3.12(a) and 3.12(b) respectively. The drains are tied together and the output is taken as common drain point as shown in the Figure 3.12(c). Input is applied at the common gate connection formed by connecting the two gates together. In this circuit, when  $V_1 = V_{cc}$ ,  $T_1$  turns ON ( $V_{gs1} > V_t$ )

and  $T_2$  is OFF since  $V_{gs2}$ =0 volt. Therefore, the quiescent power dissipation, which is the product of the OFF leakage current and  $V_{cc}$  is very small. CMOS have extremely low power dissipation and is very useful for remote applications where power is expensive. It has high noise immunity, large Fan-out, full power supply, logic swings etc,

The basic gates can be realised using CMOS ICs as described below

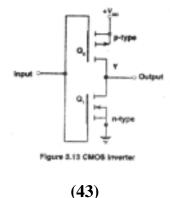

#### **CMOS Inverter**

Figure 3.13 shows the circuit diagram for CMOS inverter. If low (0V) is applied to the input,  $Q_1$  which is an n-type MOSFET is OFF and  $Q_2$  which is p-type MOSFET is O. Since MOS transistors consumes negligible power the output Y is almost equal to  $V_{DD}$  (or HIGH).

When the inverter input is high i.e. at  $+V_{DD}$  then  $Q_1$  (n-type MOS transistor) is ON and  $Q_2$  (p-type MOS transistor) is OFF. The output point Y is connected to the ground point, thus, the output is LOW (or 0V).

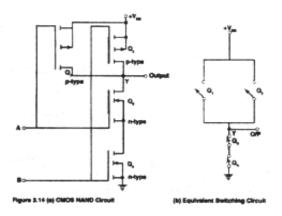

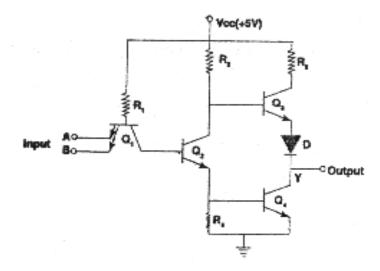

#### **CMOS NAND**

The Figure 3.14(a) shows the circuit of CMOS NAND, It can be seen that p-type  $Q_1$  and n-type  $Q_3$  MOS transistors forms one complementary pair, p-type  $Q_2$  and n-type  $Q_4$  forms another. A LOW at the gate input turns n-type MOS transistor OFF (switch open) and p-type MOS transistor ON (switch closed).

Keeping these things in mind, take up the input conditions as if A=B=0 then Q1 and Q2 will be ON and Q3 and Q4 OFF, pulls the VDD to the output point Y and thus getting high output.

If A=0 and B=1Q1 and Q4 are on and Q2 and Q3 are OFF thus point Y is at high potential.

If A=0 and B=1Q2 and Q3 are on and Q1 and Q4 are OFF thus point Y is at high potential.

If A=B=1 then Q1 and Q2 are OFF and Q3 and Q4 are ON, the output terminal Y is connected to ground terminal thus getting low output.

| Truth Table |   |                          |  |

|-------------|---|--------------------------|--|

| В           | A | Y                        |  |

| 0           | 0 | $+\mathbf{V}_{	ext{DD}}$ |  |

| 0           | 1 | $+\mathbf{V}_{	ext{DD}}$ |  |

| 1           | 0 | $+\mathbf{V}_{	ext{DD}}$ |  |

| 1           | 1 | O                        |  |

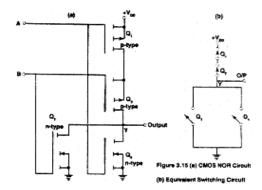

#### **CMOS NOR**

I A=B=0, then Q1 and Q2 are ON and Q3 and Q4 are OFF thus connecting the output point Y to  $V_{\rm DD}$  (high).

If A=0 and B=1, in this condition Q1 and Q3 are ON and Q2 and Q4 are OFF, thus connecting the output terminal to ground which is at 0v.

If A=1 and B=0 Q1 and Q3 are OFF and Q2 and Q4 areON, connecting the output terminal Y to ground.

If A=B=1, Q1, Q2 are OFF and Q3 and Q4 are ON thus connecting the output terminal to ground.

| Truth Table |   |           |  |

|-------------|---|-----------|--|

| В           | A | Y         |  |

| 0           | 0 | $+V_{DD}$ |  |

| 0           | 1 | 0         |  |

| 1           | 0 | 0         |  |

| 1           | 1 | 0         |  |

Table 3.9: Truth Table for CMOS NOR Gate

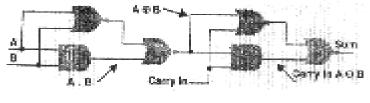

### **Applications: Logic Implementations using Gates**

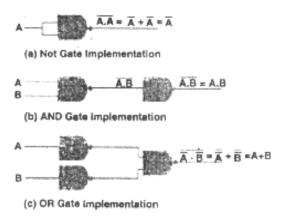

Any Boolean (or logic) expression can be realised by using the AND, OR and NOT gate. These three gates are called the basic gates. However, the NAND and NOR gate, is said to be universal gate because any of them alone is sufficient to implement any Boolean function. Because of this reason NAND and NOR gates are known as Universal gates.

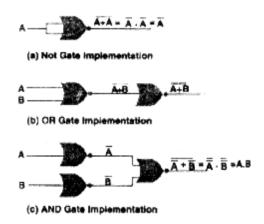

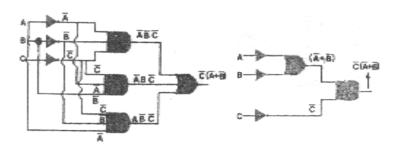

### Realization of NOT, AND, and OR Gate using NAND Gate(s)

The three basic logic operation NOT, AND, and OR can be performed by using NAND gates. This is shown in Figure 3.16.

Figure 3.16 Implementation of NOT, AND, and OR Gates by NAND Gate(s)

A NOT operation is obtained from a 1-input NAND gate. Thus, we find that a single input NAND gate behaves as an inverter. The AND operation requires two NAND gates. The first one produces the inverted AND and the second one acts as an inverter to obtain the normal AND output.

For the OR operation the normal inputs A and B are first complemented using two single input NAND gates. Now, the complemented variables are fed as input to another NAND gate, which produces the normal OR output.

### Realization of NOT, AND and OR Gate using NOR Gate(s)

The NOR function is the dual of the NAND function. For this reason, all procedures and rules for NOR logic form a dual of the corresponding procedures and rules developed from NAND logic. The logical operational NOT, AND and OR gates can be implemented solely with NOR gates as shown below in Figure 3.17

Figure 3.17 Implementation of NOT, OR, and AND Gates by NOR Gate(s)

The NOR operation is obtained from one-input NOR gate. Thus a single-input NOR gate is yet another inverter circuit. The OR operation requires two NOR gate. The first one produces the inverted OR and the second one being a single input NOT gate, acts as an inverter to obtain the normal OR output. The AND operation is achieved through a NOR gate with additional inverters in each input.

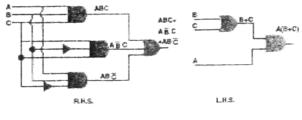

### Realization of XOR and XBIR Gate using Basic Gate(s)

Figure 3.18 (b) and 3.19(b) realizes the implementation of XOR and XNOR gate using three basic gates. Figure 3.18(a) and 3.19(a) are the symbols for XOR and XNOR.

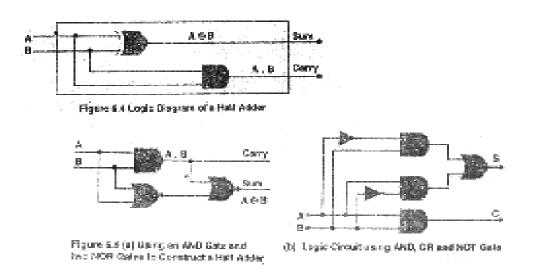

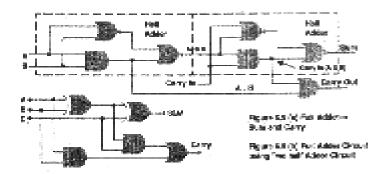

Figure 1.18 (b) Implementation of XOR Function with AND/CR/ NOT Gate(a) (e) XOR Gate

Figure 3.19 (a) XNOR Gate (b) Implementation of XNOR using Three Basic Gate(s)

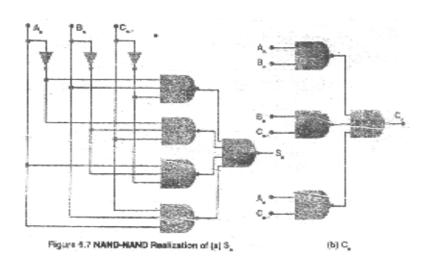

### Realization of XOR and XNOR Gate using NAND and NOR Gates

XOR and XNOR implementation is possible through universal NAND and NOR gates. Figure 3.20 and 3.21 shown the realization of XOR and XNOR through NAND gate. Similarly, XNOR gate can be represented by using NOR gates.

Figure 3.21 Implementation of XNOR Function with NAND Gale(s)

## Realization of De Morgan's Theorem through Basic Gates

Theorem1:

Theorem2:  $\overline{A + B} = \overline{A \cdot B}$

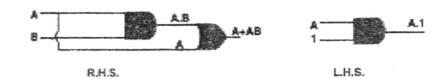

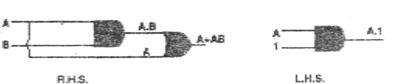

### **Assignment 1**

Prove the following rules and draw their respective circuits

- a) AC+ABC=AC

- b) A+AB=A

- c) ABC+ABC+ABC=A(B+C)

- d) A+A=1

- e) (A+B)(A+C)=AC+AB

- f) AB+AC+BC=AC+BC

- g) ABC+ABC+ABC=C(A+B)

#### **Solutions**

a) AC+ABC=AC(1+B)=AC, since 1+B=1

b) A+AB=A(1+B)=A

$(C + B\overline{C} = C + B)$

c)  $ABC + A\overline{B}C + AB\overline{C} = AC(B + \overline{B}) + AB\overline{C}$  $= AC + AB\overline{C} \qquad (B + \overline{B} = 1)$  $= A + (C + B\overline{C})$ = A + (B + C)

d) A can have only two values, 0 and 1.

When

$$A=0$$

,  $A+A=0+0=0+1=1$

When

$$A=1$$

,  $A+A=1+1=1+0=0$

Hence A+A=1 for all possible values of A.

e)

$$A\overline{A} + AC + B\overline{A} + BC = 0 + AC + B\overline{A} + BC(A + \overline{A})$$

=  $AC(B+1) + B\overline{A}(C+1) = AC + \overline{A}B$

Finding the truth tables for the left and right hand expressions as shown in following table can prove this identity. From the table it is seen that for all possible values of A, B and C

$$(A + B) (\overline{A} + C) = AC + \overline{A} B$$

| $\boldsymbol{A}$ | В | $\boldsymbol{C}$ | $\overline{A}$ | A+B | $\overline{A}$ + $C$ | (A+B) | A.C | $A\overline{B}$ | $AC$ + $\overline{A}$ |

|------------------|---|------------------|----------------|-----|----------------------|-------|-----|-----------------|-----------------------|

| 0                | 0 | 0                | 1              | 0   | 1                    | 0     | 0   | 0               | 0                     |

| 0                | 0 | 1                | 1              | 0   | 1                    | 0     | 0   | 0               | 0                     |

| 0                | 1 | 0                | 1              | 1   | 1                    | 1     | 0   | 1               | 1                     |

| 0                | 1 | 1                | 1              | 1   | 1                    | 1     | 0   | 1               | 1                     |

| 1                | 0 | 0                | 0              | 1   | 0                    | 0     | 0   | 0               | 0                     |

| 1                | 0 | 1                | 0              | 1   | 1                    | 1     | 1   | 0               | 1                     |

| 1                | 1 | 0                | 0              | 1   | 0                    | 0     | 0   | 0               | 0                     |

| 1                | 1 | 1                | 0              | 1   | 1                    | 1     | 1   | 0               | 1                     |

f)

$$AB + AC + B\overline{C} = AB(C + \overline{C}) + AC + B\overline{C} = ABC + AB\overline{C} + AC + B\overline{C}$$

$$= AC(B+1) + B\overline{C}(A+1) + AC + B\overline{C}$$

This identity can be proved by finding the Truth Tables for left and right hand expressions.

g)

$$\overline{ABC} + \overline{ABC} + A\overline{BC}$$

$= \overline{A}.\overline{C}(B + \overline{B}) + A\overline{BC}$

$= \overline{A}.\overline{C}(1) + A\overline{BC}$

$= \overline{AC} + A\overline{BC}$

$= \overline{C}(\overline{A} + AB)$

$= \overline{C}(\overline{A} + \overline{B})$

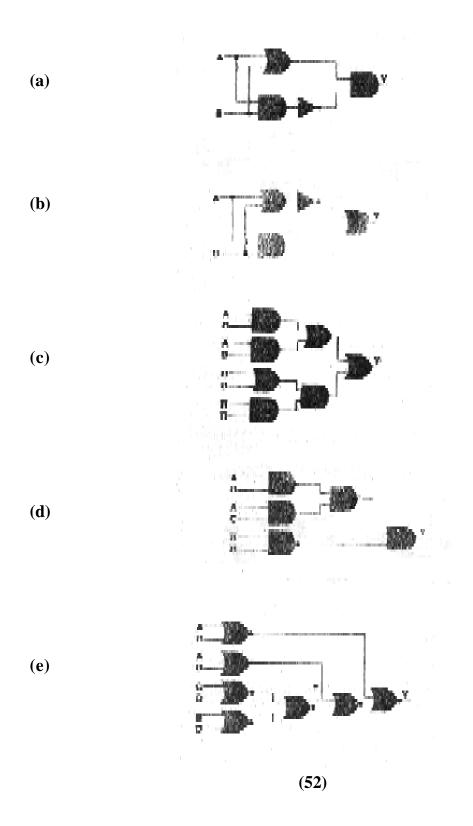

# **Assignment 2**

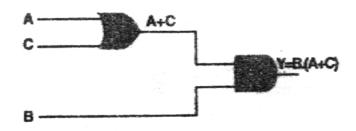

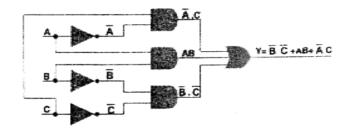

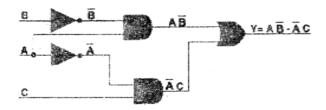

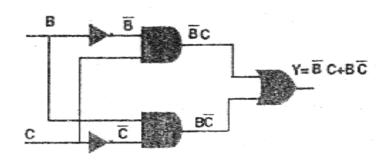

What will be the outputs for the following logic circuits?

# What will be the outputs for the following logic circuits?

### **Solutions**

(a)

$$Y = (A + B)(\overline{A}B)$$

(b)

$$Y = (\overline{A+B}) + (A.B)$$

(c)

$$Y = (AC + \overline{A}B) + C.\overline{B}.\overline{D}$$

(d)

$$Y = \overline{C} + \overline{A}B$$

(e)

$$Y = A\overline{B}C = A\overline{B}D + AC\overline{D} + BC\overline{D} + A\overline{B}$$

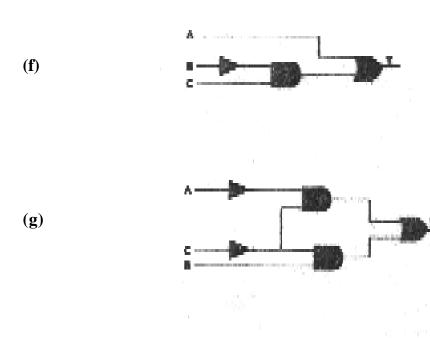

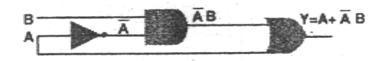

$$(f) \qquad Y = A + \overline{B}C$$

(g)

$$Y = \overline{C}(\overline{A} + B)$$

(h)

$$Y = (\overline{A} + B)\overline{C}$$

(i)

$$Y = \overline{A}BCD + A\overline{B}CD + A\overline{B}\overline{C}\overline{D} + \overline{A}B\overline{C}\overline{D}$$

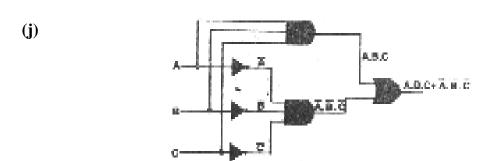

(j)

$$Y = ABC + \overline{A}\overline{B}\overline{C}$$

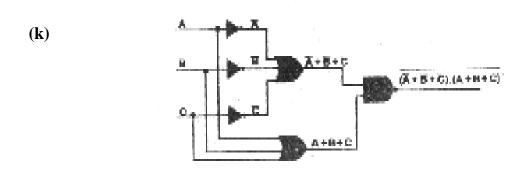

(k)

$$Y = (\overline{A} + \overline{B} + \overline{C})(A + B + C)$$

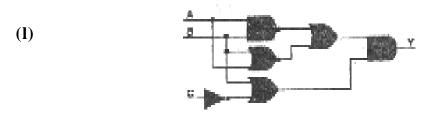

(1)

$$\overline{A}B + \overline{A}\overline{C} + \overline{B}\overline{C}$$

# **Assignment 3**

(a) Design a circuit that will implement the Truth Table given below Solution

| Input |   | Output |

|-------|---|--------|

| A     | В | Y      |

| 0     | 0 | 0      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 1      |

$Y = 0 \Rightarrow \overline{A}.B$ First line B=0A=0**Second line** A=0  $Y = 1 \Rightarrow \overline{A}.B$ B=1 $Y = 1 \Rightarrow A + \overline{A}.B$ Third line A=1B=0Fourth line  $Y = 1 \Rightarrow A + \overline{A}B$ B=1A=1

Therefore ,  $Y=A \Rightarrow \overline{A}B$

**(b)**

# **Solution**

| Inputs |   | Ou | tput |

|--------|---|----|------|

| A      | В | С  | Y    |

| 0      | 0 | 0  | 0    |

| 1      | 0 | 0  | 0    |

| 0      | 1 | 0  | 0    |

| 1      | 1 | 0  | 1    |

| 0      | 0 | 1  | 0    |

| 1      | 0 | 1  | 0    |

| 0      | 1 | 1  | 1    |

| 1      | 1 | 1  | 1    |

$Y = 0 \Rightarrow A.B.C$ First line C=0A=0B=0**Second line** A=1 C=0B=0Third line C=0A=0B=1C=0 **Fourth line** A=1B=1Fifth and Sixth line  $\Rightarrow$  ABC **Seventh line** A=0 B=1 C=1Eighth line A=1 B=1C=1  $Y = 1 \Rightarrow ABC$

### Therefore

(c)

# **Solution**

|    |        |   | V = 0 = X | $\overline{\mathbf{A}\mathbf{B}\mathbf{C}}\mathbf{B}\overline{\mathbf{C}} + \overline{\mathbf{A}}\mathbf{B}\mathbf{C} = \mathbf{B}(\mathbf{A} + \mathbf{C})$ |

|----|--------|---|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In | Inputs |   | tput      | THE - D(II   C)                                                                                                                                              |

| A  | В      | С | Y         |                                                                                                                                                              |

| 0  | 0      | 0 | 1         |                                                                                                                                                              |

| 1  | 0      | 0 | 1         |                                                                                                                                                              |

| 0  | 1      | 0 | 0         |                                                                                                                                                              |

| 1  | 1      | 0 | 1         |                                                                                                                                                              |

| 0  | 0      | 1 | 1         |                                                                                                                                                              |

| 1  | 0      | 1 | 0         |                                                                                                                                                              |

| 0  | 1      | 1 | 1         |                                                                                                                                                              |

| 1  | 1      | 1 | 1         |                                                                                                                                                              |

First line  $= \overline{A}\overline{B}\overline{C}$

Second line =  $A\overline{B}\overline{C}$

Third line = ABC

Fourth line =

$Fifth = \overline{A} \overline{B} C$

Sixth line = ABC

**Seventh line** =

Eighth line =

Therefore,

Y=

(d) Solution

| Inputs |   | Output |   |

|--------|---|--------|---|

| A      | В | C      | Y |

| 0      | 0 | 0      | 0 |

| 1      | 0 | 0      | 1 |

| 0      | 1 | 0      | 0 |

| 1      | 1 | 0      | 0 |

| 0      | 0 | 1      | 1 |

| 1      | 0 | 1      | 1 |

| 0      | 1 | 1      | 1 |

| 1      | 1 | 1      | 0 |

First line = ABC

Second line =

Third line = ABC

Fourth line =

Fifth =

Sixth line =  $A \overline{B} C$

Seventh line  $= \overline{A} B C$

Eighth line  $= \overline{A} \overline{B} \overline{C}$

Therefore,  $Y = A\overline{B} + \overline{A}C$

**(e)**

# **Solution**

| Inputs |   | Output. |   |

|--------|---|---------|---|

| A      | В | C       | Y |

| 0      | 0 | 0       | 0 |

| 1      | 0 | 0       | 1 |

| 0      | 1 | 0       | 0 |

| 1      | 1 | 0       | 0 |

| 0      | 0 | 1       | 1 |

| 1      | 0 | 1       | 1 |

| 0      | 1 | 1       | 1 |

| 1      | 1 | 1       | 0 |

First line = ABC

Second line =

Third line =

Fourth line =  $AB\overline{C}$

Fifth  $= \overline{A} \overline{B} C$

Sixth line =  $A \overline{B} C$

Seventh line = BC

Eighth line =

Therefore,  $Y = B\overline{C} + \overline{B}C$

(f) Solution

| Inputs |   | Output |     |

|--------|---|--------|-----|

| A      | В | C      | ABÇ |

| 0      | 0 | 0      | 1   |

| 0      | 0 | 1      | 1   |

| 0      | 1 | 0      | 0   |

| 0      | 1 | 1      | 1   |

| 1      | 0 | 0      | 1   |

| 1      | 0 | 1      | 0   |

| 1      | 1 | 0      | 1   |

| 1      | 1 | 1      | 1   |

Try yourself and get  $Y = \overline{B} \overline{C} + \overline{A} C$ .

Author: Vetter:

Dr. Sib Krishna Ghoshal

Dr. Devendra Mohan

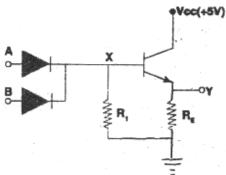

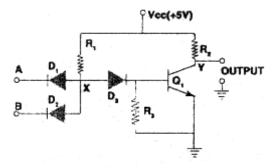

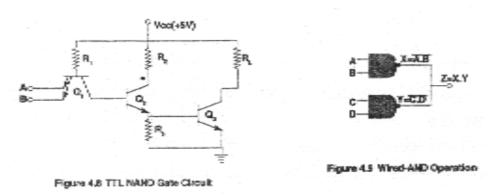

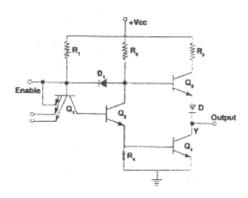

Characteristics: Fan-in, Fan-out, Propagation Delay, Noise Margin, Power Dissipation, Speed of Operation, Figure of Merit and Operating Temperature

- Logic Families: RTL, DTL, TTL and MOS Families

- Comparison of Logic Families

- Tristate Logic/Buffers

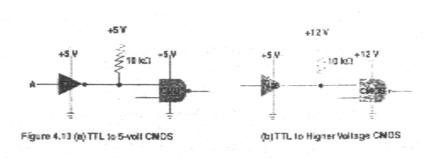

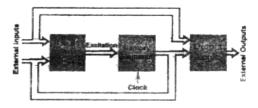

#### Introduction

An Integrated circuit is a tiny electrical device that built into a single package and performs a complete circuit function. It replaces a given number of transistors, diodes, resistors and capacitors that would be needed to perform the equivalent function.

Basically, there are two types of semiconductor devices

- 1. Bipolar (Two kind of charge carriers are involved, e. g., transistors)

- 2. Unipolar (One type of charge carrier is involved, e. g., JFET and MOSFET)

Based on these devices, digital integrated circuits have been fabricated on a single chip of silicon crystal, which are commercially available.

ICs are broadly classified into two categories

1. Linear/Analog ICs (e. g. Operational Amplifier shortly called OPAMP, whose symbolic diagram is shown in the beginning)

- 2. Digital ICs: this is further classified into two classes depending on their operation, and they are

- a) Combinational digital IC (logic gates are examples of this class)

- b) Sequential digital IC (Flip flops, multivibrator are in this category)